## XPM6136

#### 4MHz, Synchronous, 2.3V to 5.5V, 6A Ultra-Thin Power Module

## 1. Description

The XPM6136 is a fully integrated, high-frequency, synchronous, rectified, step-down, power module with internal inductor.

It offers a very compact solution to achieve 6A of continuous output current over a wide input range, with excellent load and line regulation.

Advanced Constant-on-time (COT) control operation provides very fast transient response and easy loop design, as well as very tight output regulation.

Full protection features include short-circuit protection (SCP), over-current protection (OCP) and thermal shutdown.

The XPM6136 requires a minimal number of readily available, standard external components, and is available in a space-saving LGA-24 (4mmx6mm) package.

## 2. Applications

- FPGA Power Systems

- Optical Modules

- Telecom

- Networking

- Industrial Equipment

# NC SW C1 C1 2200 C1 2200 C1 2200 C1 VNO 00T VNO C1 VNO VNO</td

Figure 1. Typical Application Circuit

## 3. Features

- Wide 2.3V to 5.5V Operating Input Range

- 6A Output Current

- Internal Power MOSFETs

- Output Adjustable from 0.5V

- Pre-Biased Start-Up

- PFM Light Load Operation for High Efficiency

- Fixed 4MHz Switching Frequency

- Soft-Start

- 100% Duty Cycle

- EN and Power Good for Power Sequencing

- Active Output Discharge

- Over-Current Protection and Hiccup Mode

- Thermal Shutdown

- Available in an LGA-24 (4mmx6mmx1.6mm) Package

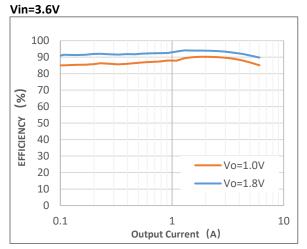

#### Figure 2. Typical Efficiency

## 4. Revision History

TABLE 1. REVISION HISTORY

| Release  | Rev | Changes | Date     |

|----------|-----|---------|----------|

| Revision | 0.8 | Updates | 11/15/23 |

# 5. Ordering Information

TABLE 2. LIST OF PARTS

| Part Number | Output Current (A) | VOUT (V)   | Top Marking | MPQ  |

|-------------|--------------------|------------|-------------|------|

| XPM6136G24R | 6                  | Adjustable | M6136       | 2500 |

|             |                    |            |             |      |

MPQ = Minimum Packaging Quantity. For production orders greater than MPQ, the order must be a multiple of MPQ per package size above.

# 6. PIN Configuration and Description

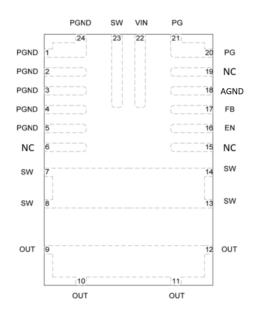

Figure 3. Top View

#### Table 3. Pin Definition

| Pin          | Name | Description                                                                                                                                                       |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2,3,4,5,24 | PGND | <b>System Ground.</b> This pin is the reference ground of the regulated output voltage.                                                                           |

| 6            | NC   | Dummy Pin.                                                                                                                                                        |

| 7,8,13,14,23 | SW   | Switch Output. This pin can be left floating.                                                                                                                     |

| 9,10,11,12,  | OUT  | <b>Output Pin.</b> Connect this pin to C <sub>OUT</sub> .                                                                                                         |

| 15           | NC   | Dummy Pin.                                                                                                                                                        |

| 16           | EN   | <b>Enable.</b> Pull EN high to enable the part. When floating, EN is pulled down to GND by internal $2M\Omega$ resistor and is disabled.                          |

| 17           | FB   | <b>Feedback.</b> Sets the output voltage when connected to the tap of an external resistor divider that is connected between output and GND.                      |

| 18           | AGND | <b>Signal Ground.</b> AGND is not internally connected to PGND, so ensure that AGND is connected to PGND in the PCB layout.                                       |

| 19           | NC   | Dummy Pin.                                                                                                                                                        |

| 20,21        | PG   | <b>Power-Good Output.</b> The output of this pin is an open-drain output. Its state changes if OCP, SCP, or OTP occurs.                                           |

| 22           | VIN  | <b>Supply Voltage.</b> The part operates from a 2.3V to 5.5V input rail. C1 is necessary to decouple the input rail. Use a wide PCB trace to make the connection. |

## 7. Absolute Maximum Ratings

TABLE 4. ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Parameter                                  | Min   | Max                   | Units |

|--------------------------------------------|-------|-----------------------|-------|

| DC Supply Voltage, VIN                     | -0.3  | +7.0                  | V     |

| SW (10ns transient)                        | -0.3  | +8.0                  | V     |

| Voltage on other pins, PG, SW, FB, EN, OUT | -0.3  | V <sub>IN</sub> + 0.3 | V     |

| Storage Temperature Range                  | -40   | +150                  | °C    |

| Junction Temperature                       | -40   | +150                  | °C    |

| Electrostatic Discharge (HBM)              | -2000 | 2000                  | V     |

| Electrostatic Discharge (CDM)              | -2000 | 2000                  | V     |

# 8. Recommended Operating Conditions

| Parameter                       | Symbol          | Min | Тур  | Max              | Units |

|---------------------------------|-----------------|-----|------|------------------|-------|

| Supply Voltage                  | VIN             | 2.3 |      | 5.5 <sup>2</sup> | V     |

| Output Current                  | Іоит            | 0   |      | 6.0              | А     |

| Input Capacitor                 | CIN             | 10  | 22   |                  | μF    |

| Output Capacitor                | Соит            | 22  | 3*22 |                  | μF    |

| Operating Temperature, Junction | T <sub>OJ</sub> | -40 |      | +125             | °C    |

## TABLE 5. OPERATING CONDITIONS

#### TABLE 6. THERMAL INFORMATION

Junction to ambient thermal resistance is a function of board layout and ambient air flow condition. The data below is based on XPM6136 four-layer evaluation board in still air box in accordance to JEDEC standard JESD51 on natural convection.

| Parameter                              | Symbol | Тур   | Units |  |

|----------------------------------------|--------|-------|-------|--|

| Junction-to-Ambient Thermal Resistance | θ」Α    | 23.93 | °C/W  |  |

| Junction-to-Case Thermal Resistance    | θις    | 7.66  | °C/W  |  |

<sup>&</sup>lt;sup>1</sup> Operation of the device outside of these parameters may cause permanent damage.

<sup>&</sup>lt;sup>2</sup> Vin above 5.5V over extended periods may affect device reliability.

## 💓 ХІЛЛІ ТЕСН

# 9. Electrical Specifications

| Parameter                         | Symbol               | Condition                                                | Min | Тур   | Max | Units |

|-----------------------------------|----------------------|----------------------------------------------------------|-----|-------|-----|-------|

| Input voltage range               | VIN                  |                                                          | 2.3 |       | 5.5 | V     |

| Supply Current                    |                      |                                                          |     |       |     | •     |

| Supply current (shutdown)         | Ishdn                | V <sub>EN</sub> = 0V                                     |     | 3     |     | μΑ    |

| Supply current (quiescent)        | Ια                   | No Load, Not Switching                                   |     | 40    |     | μΑ    |

| Current Limit                     |                      |                                                          |     |       |     | •     |

| PMOS Peak Current Limit           | ILIM                 | V <sub>IN</sub> = 3.3V, Open Loop                        |     | 9     |     | А     |

| Switching Frequency               |                      |                                                          |     |       |     |       |

| Switching Frequency               | Fsw                  |                                                          |     | 3     |     | MHz   |

| Reference and Soft Start          |                      |                                                          |     |       |     | •     |

| Feedback Voltage                  | V <sub>FB</sub>      | T <sub>J</sub> = -40°C to +125°C                         | 495 | 500   | 505 | mV    |

| Feedback Current                  | I <sub>lkg(FB)</sub> | V <sub>FB</sub> = 0.6V                                   |     | 5     |     | nA    |

| Soft-Start Time                   | Tss                  |                                                          |     | 3     |     | ms    |

| Enable                            | -                    | •                                                        | •   |       |     |       |

| Logic High Voltage                | VIH                  |                                                          | 1.2 |       |     | V     |

| Logic Low Voltage                 | VIL                  |                                                          |     |       | 0.5 | V     |

| Logic Input Hysteresis            | VLHYST               |                                                          |     | 250   |     | mV    |

| Logic Pin Leakage Current         | I <sub>LPIN</sub>    |                                                          |     | 2.5   |     | μA    |

| EN pin pull-down resistor         | R <sub>EN_PD</sub>   |                                                          |     | 2     |     | MΩ    |

| Enable Turn-on Delay              | T <sub>EN</sub>      |                                                          |     | 100   |     | μs    |

| UVLO                              |                      |                                                          |     |       |     |       |

| Under-Voltage Lockout Threshold   | VUVLO                | Rising V <sub>IN</sub>                                   |     | 2.0   | 2.2 | V     |

| Under-Voltage Lockout Hysteresis  | VUVLOHYST            |                                                          |     | 200   |     | mV    |

| Power Good                        |                      |                                                          |     |       |     |       |

| Power Good Threshold Vout Rising  | Vpgr                 | V <sub>FB</sub> referenced to V <sub>FB</sub><br>nominal |     | 96.5% |     |       |

| Power Good Threshold Vout Falling | Vpgf                 | V <sub>FB</sub> referenced to V <sub>FB</sub><br>nominal |     | 92.5% |     |       |

| Power Good Low Voltage            | Vpgl                 |                                                          |     |       | 100 | mV    |

| Power Good Leakage Current        | IPG                  |                                                          |     | 3     |     | nA    |

| Power Switches                    |                      | •                                                        | •   |       |     |       |

| PMOS On Resistance                | Rdsonp               | $V_{IN} = V_{GS} = 3.3V$                                 |     | 12    |     | mΩ    |

| NMOS On Resistance                | Rdsonn               | $V_{IN} = V_{GS} = 3.3V$                                 | Ì   | 7.5   |     | mΩ    |

| Dropout Resistance                | R <sub>DP</sub>      | 100% mode, Vin = 2.7V                                    |     | 22    |     | mΩ    |

| Output Discharge Resistance       | R <sub>DIS</sub>     | EN = OV                                                  |     | 17    |     | Ω     |

| Thermal Protection                | -                    |                                                          | •   |       |     |       |

| Thermal Shutdown                  | T <sub>SD</sub>      |                                                          |     | 150   |     | °C    |

| Thermal Hysteresis                | T <sub>SD-HYS</sub>  |                                                          |     | 20    |     | °C    |

Typical values unless otherwise noted:  $V_{IN}$  = 3.3V,  $V_{OUT}$  = 1.8V, Temp = +25°C

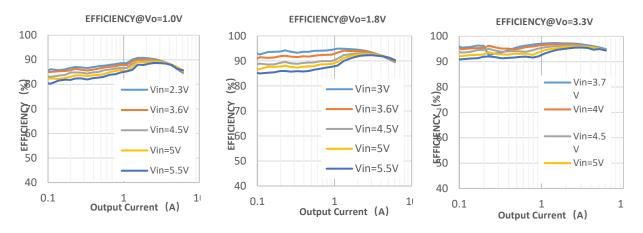

## 10. Typical Performance and Operating Characteristics

## 11. Functional Descriptions

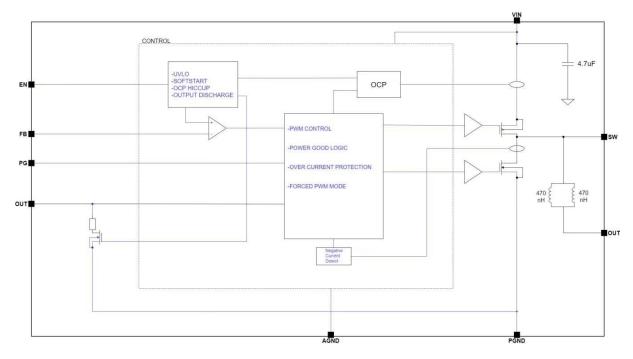

Figure 4. Functional Block Diagram

The XPM6136 is a synchronous DC/DC power module integrated with power inductor. Operating from an input voltage between 2.3V and 5.5V, the power module can deliver up to 6A of load current. With 4MHz typical switching frequency and Advance Constant-on-time (ACOT), it provides fast load transient response performance and excellent DC voltage regulation.

## Enable

Setting the EN pin to logic High enables the device. Alternatively, the device is disabled when the EN voltage is set to logic Low. In this state the IC draws less than  $3\mu$ A of current and the output is pulled to ground through a resistive load. V<sub>OUT</sub> starts to ramp up after 100µs delay.

When floating, EN is pulled down to GND by an internal  $2M\Omega$  resistor.

## Soft-Start

When the device is enabled, internal soft-start circuitry causes  $V_{OUT}$  to ramp up over a period of 3ms to limit inrush current. This feature protects a high impedance source from being pulled to a lower voltage as the device turns on.

## Under voltage Lockout (UVLO)

The under-voltage lockout feature prevents the device from turning on if  $V_{IN}$  is below the UVLO level of 2.0V. If the device is enabled under UVLO conditions, the circuitry will not turn on until the input voltage

#### 4MHz, Synchronous, 2.3V to 5.5V, 6A Ultra-Thin Power Module

is increased. Once active, the UVLO circuit has 200mV of hysteresis and the device will turn off if V<sub>IN</sub> drops below 1.8V.

#### Active Output Discharge

When the device is disabled through the EN pin, a discharge path for the output capacitor is created between  $V_{OUT}$  and ground through a 17 Ohm resistor ( $R_{DIS}$ ).

#### Modes of Operation

XPM6136 employs advance constant-on-time control, its switching frequency is nearly constant at 4MHz at high current loads.

If the input voltage ever gets too close to the target output voltage, such that regulation can no longer be maintained, the regulator will enter 100% duty cycle mode. In this mode the high side switch is ON, connecting the input and output together to deliver a voltage as close to the target as possible.

#### Thermal Shutdown

The device thermal shutdown protection is enabled if the chip temperature exceeds 150°C. Once the temperature drops below 130°C, the device will be re-enabled, and a new soft-start cycle will begin.

#### **Over current Protection**

The device has over current protection to prevent damage to the device and inductor during over current conditions.

Peak current protection occurs at 9A. After hitting 16 consecutive cycles of peak current limit, the output will be disabled. After being disabled for 1.5ms, the device will be re-enabled, and a new soft-start cycle will begin.

#### **Power Good Indicator**

The PG pin is an open-drain output and pulls the PG pin low when the FB voltage is less than 92% of the nominal internal reference voltage and resumes when FB voltages is greater than 96% of the nominal internal reference voltage.

## 12. Layout Guidelines and Example

A well-designed and manufactured PCB is important for all switching power supplies, especially for those operate at high switching frequency.

If the layout is not fulfilled carefully, not only regulator performance could be degraded but also stability or EMI issue may be introduced. Hence, care must be taken in board layout to achieve the specified performance.

Please use the following guidelines when designing PCBs:

1) Keep components placement as compact as possible.

- 2) Place a low-ESR input capacitor as close to VIN and GND as possible.

- 3) Keep FB trace away from noisy components and traces (e.g., SW and inductor).

- 4) Use wide and short traces for the main current paths.

## 4MHz, Synchronous, 2.3V to 5.5V, 6A Ultra-Thin Power Module

5) Ground pins of regulator must be strongly connected to PCB ground with low inductance and impedance.

6) Place common and unbroken ground for CIN and COUT.

7) Reduce excessive thermal relief vias and keep them away from SW and inductor.

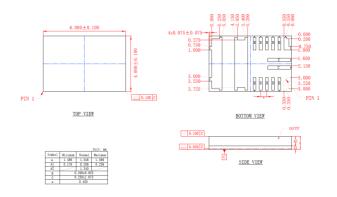

## 13. Physical Dimensions

## LGA-24 (4mm\*6mm\*1.6mm)

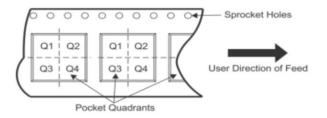

# 14. Tape and Reel Information

## Pin 1 located in Q1 direction in T&R

💓 ХІЛЛІ ТЕСН